I still remember lifting a Neuromorphic computing chip out of its foam and inhaling the scent of silicon tangled with solder fumes. The lab hummed with cooling fans while a colleague whispered, “This will change everything,” and I rolled my eyes—another hype line. Those early Neuromorphic computing chips felt like a handful of nervous fireflies, flickering between order and chaos. What mattered that night was the chip’s spiking neurons firing in time, mimicking a brain’s jittery rhythm instead of marching through a deterministic pipeline. It was a proof that computation can be chaotic too, and felt far more exciting than any glossy press release.

From that moment on I stopped polishing hype and began gathering the details that matter to engineers, hobbyists, and anyone who’s ever been burned by lofty promises. In the next few pages I’ll walk you through how neuromorphic computing chips can slash power budgets, the pitfalls you’ll hit when training them with conventional tools, and the design tricks that turned my prototype from curiosity into a usable accelerator. No jargon‑heavy theory—just the lessons I wish I’d known before I spent my paycheck on a “brain‑chip” demo.

Table of Contents

- When Silicon Starts to Think Neuromorphic Computing Chips Unveiled

- Lowpower Ai Accelerators Energysaving Superpowers at the Edge

- Spiking Neural Network Hardware How Eventdriven Signals Mimic Neurons

- Edge Intelligence Reinvented Braininspired Chip Architecture for Tomorrow

- Memristorbased Synaptic Circuits the Plastic Heart of Braininspired Chips

- Neuromorphic Processors for Edge Devices Eventdriven Computing Efficiency U

- 5 Pro Tips for Riding the Neuromorphic Wave

- Key Takeaways

- Silicon with a Soul

- Wrapping It All Up

- Frequently Asked Questions

When Silicon Starts to Think Neuromorphic Computing Chips Unveiled

If you’re itching to get hands‑on with a spiking‑network simulator, the open‑source project I’ve been tinkering with lately offers a tidy Python wrapper that lets you map SNN layers onto a commercial neuromorphic evaluation board; the documentation is surprisingly clear, especially the step‑by‑step guide that walks you through configuring event‑driven inference on a low‑power edge device. For a visual walkthrough, the creator’s GitHub wiki even links to a short video series hosted on a community site called scottish milf, where the author demos real‑world use cases ranging from sensor‑fusion to on‑chip learning—trust me, that walkthrough saved me a weekend of head‑scratching and is a great way to see spiking neural networks move from theory to silicon.

Imagine a silicon lattice that doesn’t just crunch numbers but listens to the rhythm of spikes, mimicking the way neurons fire in our cortex. Spiking neural network hardware leverages this timing, letting each pulse trigger computation only when there’s something to say, which slashes idle power draw dramatically. Pair that with a brain‑inspired chip architecture—layers of artificial dendrites and axons woven into a compact die—and you get a platform where data arrives as events rather than a relentless stream of bits. The result is event‑driven computing efficiency that can outpace conventional GPUs on tasks that thrive on sparsity, such as real‑time sensory processing or on‑device speech recognition.

Beyond the lab, these designs are spilling over into the wild frontier of edge AI. By integrating low‑power AI accelerators directly onto tiny sensor nodes, engineers can embed true intelligence into wearables, drones, and remote cameras without draining a battery in minutes. The secret sauce often lies in memristor based synaptic circuits, which store weight values in analog resistance states, letting the chip “remember” patterns without a separate memory fetch. When such neuromorphic processors for edge devices finally hit the market, we’ll see smart cameras that flag anomalies on the spot, phones that adapt to a user’s voice in seconds, and robots that navigate cluttered rooms with a brain‑like intuition—all thanks to silicon finally learning to think.

Lowpower Ai Accelerators Energysaving Superpowers at the Edge

Imagine a tiny sensor stuck on a drone that can recognise a fire‑hazard in real time without draining its battery. That’s the promise of low‑power AI accelerators: chips that squeeze neural inference into a few milliwatts, letting edge devices stay awake longer and react faster. By arranging compute units around a spike‑driven dataflow, they avoid the constant clock‑tick that wastes energy. Because every milliwatt saved translates into minutes of flight time for a battery‑limited UAV.

Manufacturers achieve this thriftiness by flirting with near‑threshold voltages and harvesting the natural sparsity of modern deep‑learning models. A single accelerator can run a full‑frame object detector while sipping power comparable to a LED night‑light. The result? Robots, wearables, and remote sensors finally get the brainpower they need without dragging a generator along. That efficiency opens doors for AI‑driven health monitors in remote clinics today now.

Spiking Neural Network Hardware How Eventdriven Signals Mimic Neurons

At the heart of spiking‑based chips lies an event‑driven architecture that throws out the clock‑driven tyranny of conventional processors. Instead of marching every transistor through a uniform rhythm, the hardware wakes only when a digital “spike” arrives—just like a neuron firing an action potential. This on‑demand activation means idle gates stay silent, slashing power draw while preserving the precise timing cues that biological brains rely on.

Because spikes are sparse in time, the chips can harvest temporal sparsity as a resource rather than a limitation. Intel’s Loihi, for instance, stores synaptic weights locally and only updates them when a spike traverses a synapse, letting the processor skip millions of unnecessary cycles. The result is a system that not only mirrors neuronal communication but also scales its energy budget with the very information it processes. That efficiency opens doors for edge‑AI gadgets lasting days.

Edge Intelligence Reinvented Braininspired Chip Architecture for Tomorrow

When a sensor‑rich camera or a tiny wear‑able needs to make split‑second decisions, brain‑inspired chip architecture steps into the spotlight. By wiring together spiking neural network hardware with memristor‑based synaptic circuits, these processors mimic the way biological neurons fire only when a threshold is crossed. The result is a dramatically lean power envelope: low‑power AI accelerators can run inference at a fraction of the energy budget of conventional GPUs, making real‑time vision, speech, or anomaly detection feasible on a battery‑powered edge node. Because the circuitry only wakes up on meaningful spikes, the whole system behaves like a nervous system that stays quiet until something matters.

Beyond raw efficiency, the design opens doors for true event‑driven computing efficiency across the Internet of Things. Neuromorphic processors for edge devices can stream data directly into a spiking fabric, bypassing the costly shuffle between memory and compute that plagues von‑Neumann chips. This tight integration means a smart thermostat, a drone, or a medical implant can continuously adapt to its environment without draining a single charge, turning every peripheral into a miniature brain that learns on the fly. The era of autonomous, ultra‑low‑power AI at the edge is no longer a fantasy—it’s being built brick by brick on these innovative, brain‑like silicon foundations.

Memristorbased Synaptic Circuits the Plastic Heart of Braininspired Chips

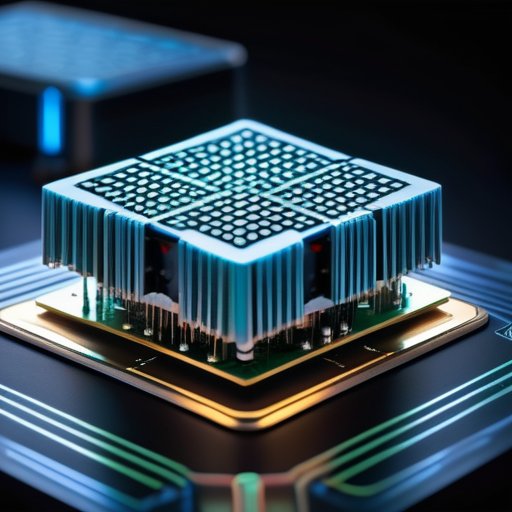

What makes a neuromorphic chip feel alive is the way it stores and forgets information, and that job falls to the memristor. These resistors remember their past resistance state, so when a voltage spike arrives they adjust their conductance like a biological synapse that strengthens or weakens. By arranging millions of them in cross‑bar arrays, engineers can sculpt a plastic heart that rewires itself on the fly.

Beyond mimicking biology, memristor‑based synapses give the chip a built‑in analog memory, eliminating the need for costly digital look‑up tables. When a spike‑timing‑dependent learning rule fires, the device nudges its conductance, encoding a weight directly into the material. The result is a low‑power, non‑volatile synapse that can sit idle for months yet spring back with a single pulse—exactly the analog weight storage that lets edge devices think for days on a battery.

Neuromorphic Processors for Edge Devices Eventdriven Computing Efficiency U

When a sensor flickers, a neuromorphic engine wakes only for that spike, skipping idle cycles entirely. This event‑driven architecture means an edge node can run for weeks on a coin‑cell battery, because every operation is tied to a real‑world change rather than a clock tick. The result is a silicon brain that scales its power draw with the world’s activity, turning otherwise wasteful polling into purposeful computation.

Beyond power savings, the same chips exploit asynchronous processing to cut latency. When a camera detects motion, the processor streams the spike straight to a local AI core, skipping the usual frame‑grab‑and‑buffer pipeline. The edge device therefore reacts in microseconds, enabling real‑time safety alerts or instant voice wake‑words without ever waking a heavyweight GPU. Thermal footprints stay whisper‑quiet, even in cramped IoT hubs for deployment.

5 Pro Tips for Riding the Neuromorphic Wave

- Start with a small, event‑driven test board before scaling up to full‑system designs.

- Match your memory technology (e.g., memristors or phase‑change devices) to the spike‑driven workload for maximum energy gain.

- Embrace asynchronous clocking; letting spikes dictate activity cuts idle power dramatically.

- Leverage on‑chip learning rules (STDP, Hebbian) to keep firmware updates lightweight and adaptable.

- Keep thermal design in mind—spiking architectures can concentrate heat in dense cross‑bar arrays, so plan for efficient heat‑spreading early.

Key Takeaways

Neuromorphic chips turn spikes of data into brain‑like processing, slashing power use while keeping latency ultra‑low.

Memristor‑based synapses give hardware the ability to “learn” on the fly, blurring the line between memory and compute.

Edge devices equipped with event‑driven neuromorphic processors can run sophisticated AI locally, unlocking real‑time intelligence without cloud dependence.

Silicon with a Soul

“Neuromorphic chips don’t just compute—they whisper the rhythm of neurons, turning silicon into a living, breathing partner for every edge device.”

Writer

Wrapping It All Up

Throughout this piece we’ve seen how neuromorphic chips turn silicon into a miniature brain, using spiking neural networks that fire only when a signal arrives, just as a neuron does. By leveraging event‑driven computation, these chips slash the power draw that plagues traditional GPUs, delivering energy‑efficient AI right at the edge. The memristor‑based synaptic arrays act as the plastic heart of the system, rewiring themselves on the fly to store learned weights. Together, they enable ultra‑low‑latency inference for everything from autonomous drones to smart wearables, proving that the marriage of neuroscience and semiconductor engineering can finally break the energy wall that has limited edge AI for years.

The real excitement lies not just in the technical triumphs but in the societal ripple they create. Imagine a world where remote villages run AI‑powered health monitors, where autonomous robots navigate disaster zones without draining a battery, and where personal devices understand our gestures in real time—all thanks to brain‑inspired edge intelligence. As the cost of memristor fabrication drops and design tools mature, the barrier to entry for startups and researchers will dissolve, democratizing access to sustainable AI. The next decade could see neuromorphic processors woven into every sensor‑rich environment, turning everyday objects into quiet, thinking companions that learn, adapt, and respect our planet’s limited energy budget. And that, perhaps, is the true promise of silicon that truly thinks.

Frequently Asked Questions

How do neuromorphic chips differ from traditional CPUs and GPUs in terms of architecture and energy efficiency?

A CPU is a busy clerk—fetch, decode, execute every clock tick, even when idle. A GPU is a factory line, parallelizing the same task across many cores. Neuromorphic chips act like a brain: they fire only on incoming spikes, using tiny memristor synapses that store weights locally. Because they’re event‑driven, power scales with activity, letting a coin‑cell run them for days, whereas a CPU would drain it in minutes—or even weeks on low‑load tasks.

What are the biggest challenges in programming and developing software for spiking neural network hardware?

Programming spiking‑neural hardware feels like learning a new dialect of code. First, you must ditch the familiar frame‑based mindset and think in discrete events—every spike is a timestamped message. Second, the lack of mature toolchains forces you to cobble together custom simulators, debuggers, and profilers. Third, mapping algorithms onto ultra‑low‑power neuromorphic architectures requires timing constraints and careful management of limited on‑chip memory. Finally, the scarcity of standardized libraries makes portability across different chips a climb.

Which real‑world edge devices are already leveraging neuromorphic processors, and what benefits are they seeing?

A handful of edge gadgets are already running on neuromorphic silicon. Intel’s Loihi‑based “Neuro‑Drone” prototype can react to obstacles in real time while sipping less than a milliwatt of power, letting it stay aloft longer. Sony’s Spiking‑Vision chip lives inside a smart security camera, processing every pixel as an event rather than a full frame, which slashes bandwidth and cuts energy use by up to 80 %. Meanwhile, BrainChip’s Akida‑powered IoT sensor performs on‑device keyword spotting without ever waking a heavyweight CPU, extending battery life from days to weeks. In each case, the key wins are ultra‑low power, latency‑free inference and the ability to run AI directly where data is generated.